Modificare surse ATX => Proiect didactic

Salutari tuturor.

Acest articol o sa fie unul destul de lung si prezint scuze daca plictisesc, insa scindarea sa ar fi fost contraproductiva asa ca am ales sa pun totul intr-o singura prezentare care sa trateze pas cu pas fiecare aspect al modificarii ca la carte a unei surse ATX, procedurile prezentate aici daca sunt respectate intocmai, garanteaza practic succesul oricarei conversii.

In acest subiect o sa descriu pas cu pas ceea ce este de facut pentru modificarea unei surse ATX semipunte cu integrat TL494 intr-una de laborator ( sau orice alt scop ), voi executa eu modificarea respectiva si voi explica la fiecare pas ceea ce am facut. Evident se poate si cu alt controller prin defrisari masive si adaugarea unei placute, dar cele cu TL494 sunt mai simplu de modificat deoarece ofera deja mare parte din arhitectura necesara direct pe placa.

In cazul de fata scopul este obtinerea unei surse cu o singura iesire de 35V la 3A cu protectie de tip stop ( sursa care spre exemplu poate alimenta un regulator liniar spre exemplu ), evident ca se pot obtine si alte combinatii dar eu o aleg pe asta pentru simplitate, contand in primul rand principiile care duc la acest rezultat, si mai putin rezultatul in sine.

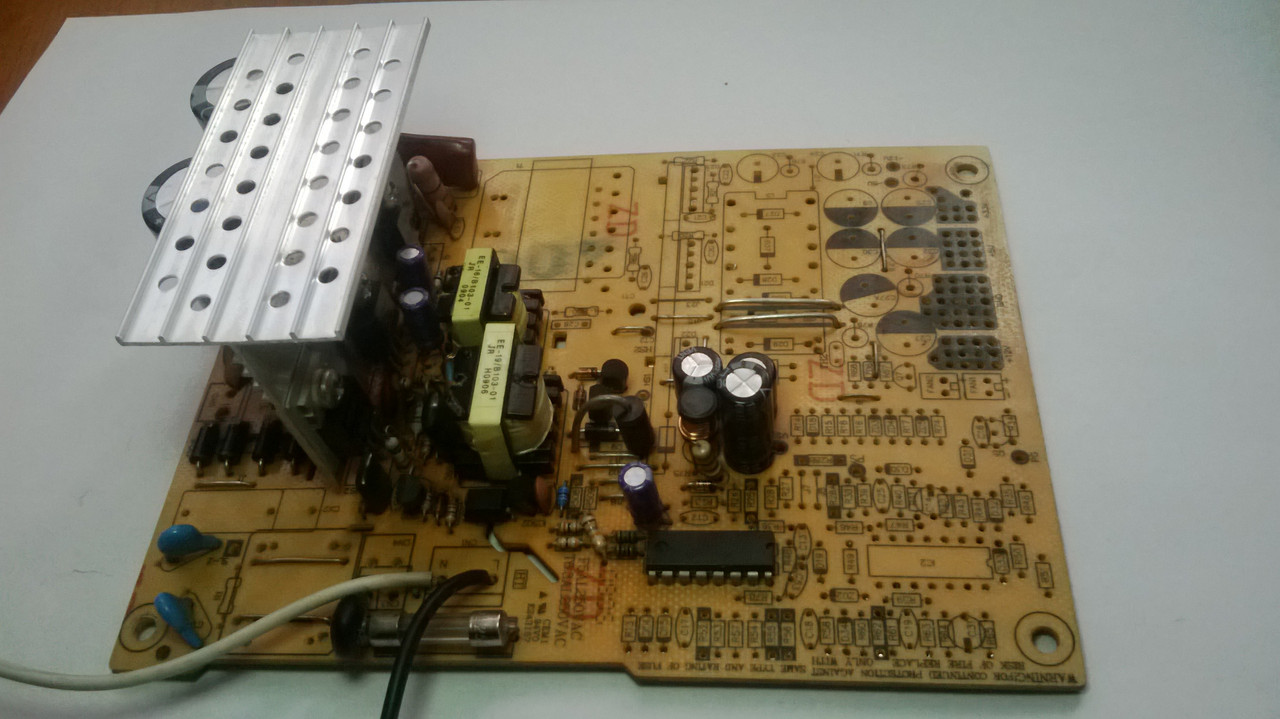

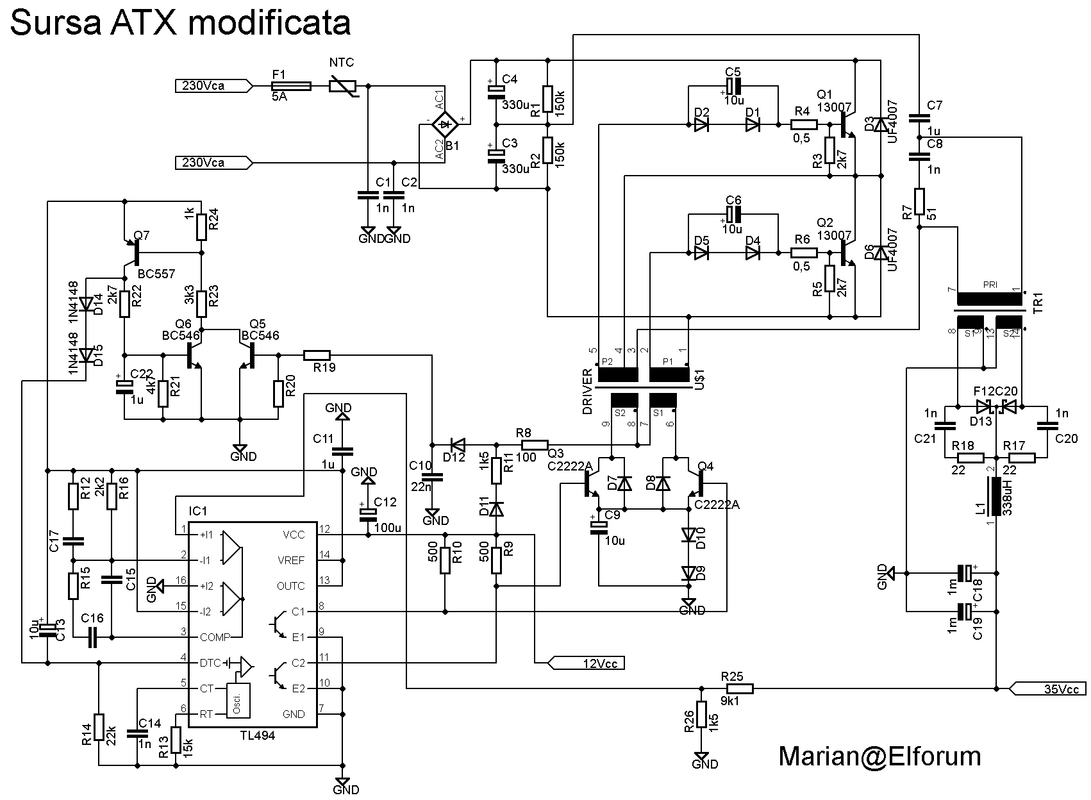

Primul pas este alegerea sursei donatoare evident, in cazul meu asadar una no-name cu K7500:

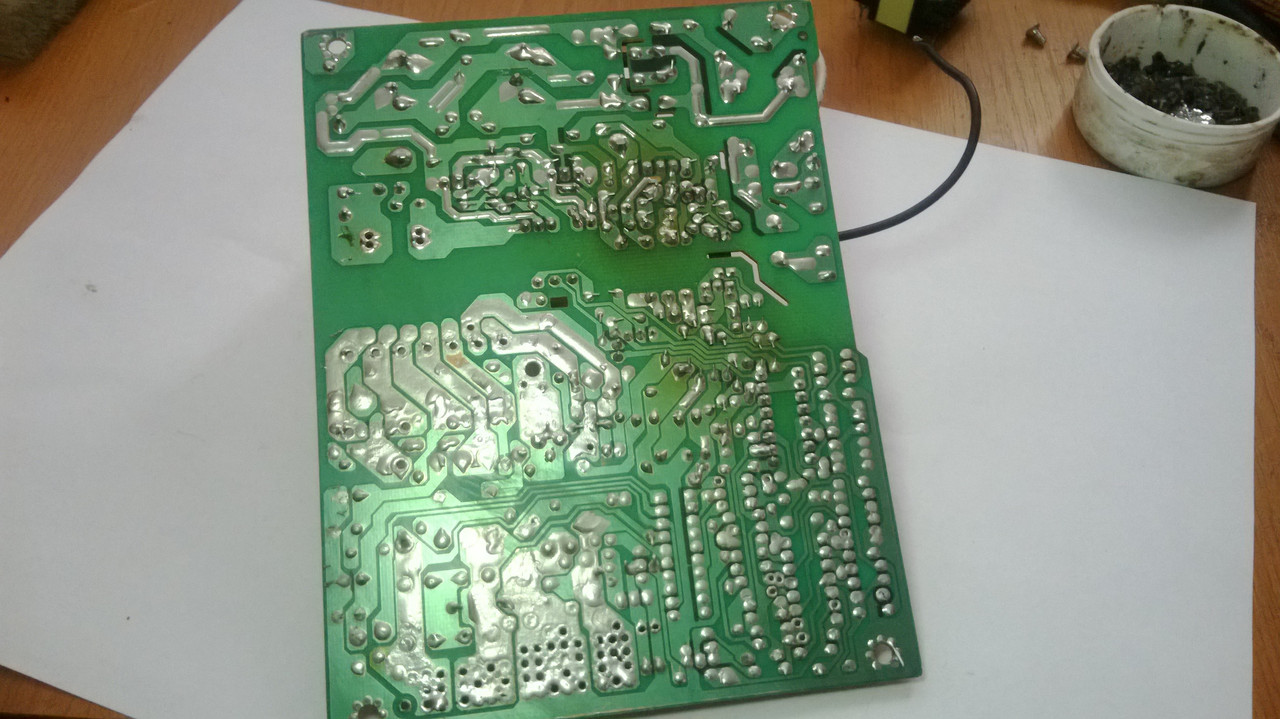

Se trece la defrisarea relativ integrala a secundarelor si a partii de control:

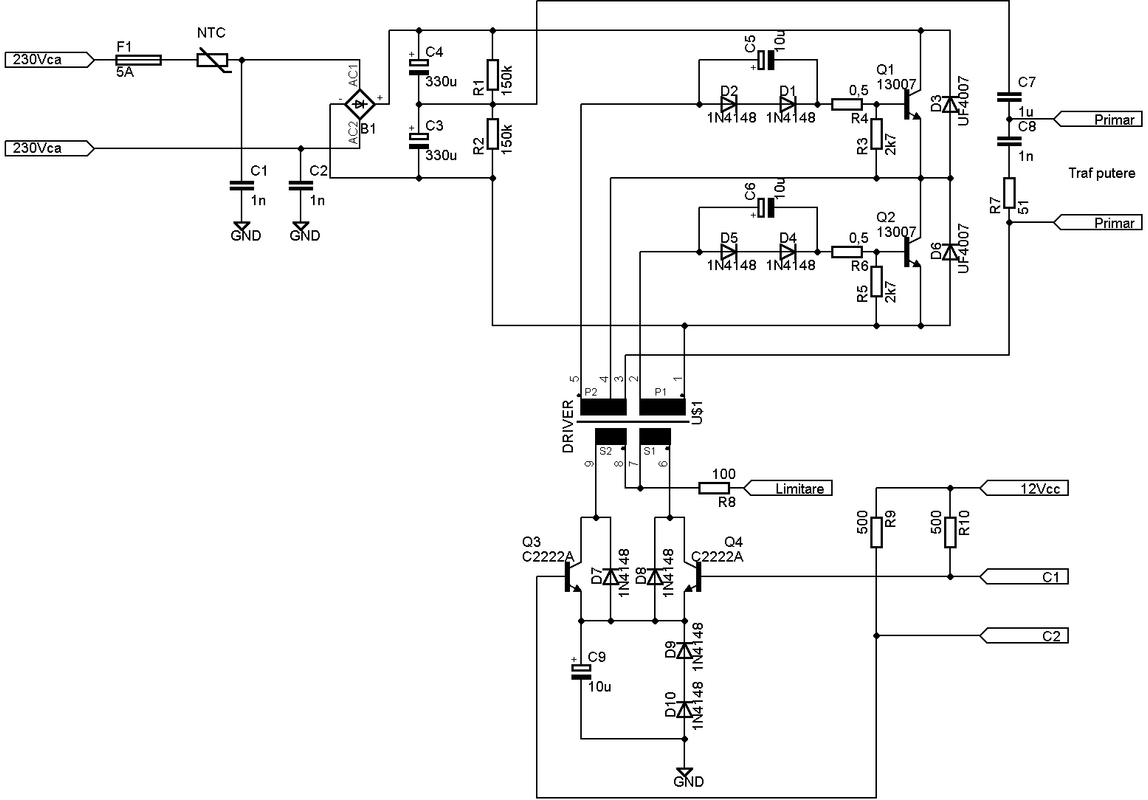

Si ignorand sursa auxiliara, se obtine relativ cam aceasta schema ( cu ceva mici variatii uneori ):

Ca tot am amintit de sursa auxiliara, la mine au fost necesare ceva interventii, un cond busit in primar inlocuit si ceva modificari in bucla constand in mutarea stabilizarii pe iesirea de 12V. Dupa ce m-am asigurat ca flyback-ul functioneaza ok am mers mai departe.

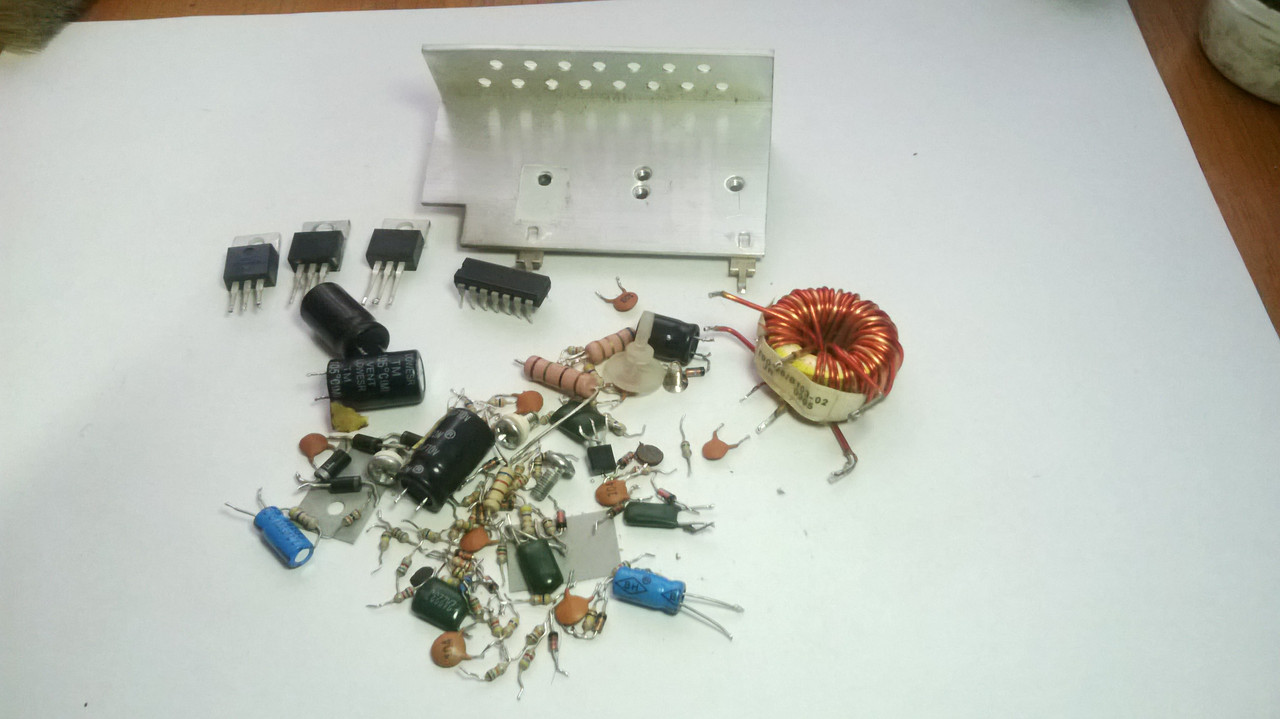

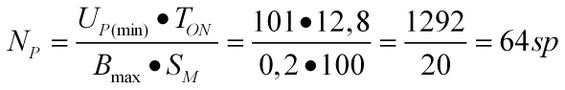

Pasul urmator este bobinarea trafului de putere, care este acesta:

Dupa vre-o 10 minute de fierbere in apa s-a desfacut destul de usor, al meu este EE35 ( sau cel putin asa scrie pe el ), are o sectiune a miezului de 100mm^2 ( miez rotund ). Alegem o frecventa la care sursa va functiona si trecem la treaba, eu am ales o combinatie RT-CT de 15k si respectiv 1n ceea ce reprezinta o frecventa a oscilatorului de cca 73Khz, deci 36,5Khz pe traf.

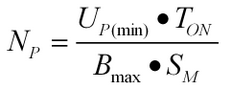

Acum alegem formula dupa care vom calcula traful, si eu merg de obicei pe:

Si avem asa:

-Upmin este tensiunea minim estimata in primar, se exprima evident in Volti;

-Ton este timpul de conductie pentru fiecare tranzistor, se exprima in uS;

-Bmax este inductia maxim admisa in miezul trafului se exprima in Tesla;

-Sm este sectiunea miezului magnetic, se exprima in mm^2;

Upmin, este tensiunea corespunzatoare retelei minime la care dorim ca sursa sa poata functiona corect, in acest punct se ia in considerare umplere maxima, sa zicem ca dorim ca la retea minima de 180Vca, sursa sa poata functiona totusi corect. Puterea dorita la iesire ar fi 105W, estimand un randament per ansamblu de sa zicem 80% asta presupune o putere in primar de 130W care corespunde unui curent de cca 0,7A extras din reteaua de 180Vca. In schema mea intre redresare si retea am un NTC la care am masurat la temperatura camerei 5 Ohm, pe astia ii iau in considerare pentru a estima pierderea pe el ( in practica va fi mai putin, el incalzindu-se dar nu strica sa fim generosi ), deci avem 3,5V picati pe NTC, ne mai raman 176,5Vca dupa el si deci la intrarea in puntea redresoare, pe aceasta din urma mai pica aproximativ 1,4V deci raman 175V care ridicati la varf de electroliticii de filtrare devin 247Vcc.

De aici impartim tensiunea asta pe jumatate si avem 2 ramuri de +/-123,5Vcc. Am zis mai devreme ca puterea estimata in primar ar fi 130W, aceasta putere va fi extrasa din fiecare ramura pe rand, deci curentul respectiv ar fi cam 1A. Acuma avem electrolitici de 330u, acestia sustin un curent de 1A la impulsurile de 10mS caracteristice redresarii retelei in punte, cu un riplu de 30Vvv, luam in considerare o medie pe care o scadem din ramura de 123,5V si raman 108,5V. Mai departe in calea catre primar avem tranzistorii, in cazul de fata banalii ST13007, care la 1A vad ca au o tensiune CE de saturatie de 1,5V, deci mai raman 107V. Inseriat cu primarul avem un condensator de 1u pe care inevitabil avem ceva pierderi, frecventa pe traf am zis ca este 36,5Khz, deci perioada de 27,4uS, umplerea maxima este in configuratia asta ( frecventa oscilator si respectiv valoare CT ) de cca 94% deci perioada scade la 25,7uS, si Ton pentru fiecare ramura este de 12,8uS, avem nevoie de cifra asta pentru determinarea riplului pe condul inseriat cu primarul si deci avem aproximativ 12,8Vvv, scadem media din cei 107V si raman 101V pentru primar ca si Upmin.

Ton este timpul cat fiecare tranzistor conduce, si se afla dupa frecventa de lucru pe traf si umplerea maxim posibila, am descris detaliat mai sus, sunt acele 12,8uS.

Bmax il estimam din pdf-ul materialului din care este realizat traful, asta ce-l am eu nu scrie pe el, dar merg pe premisa ca este 3C90 ( fiind cele mai des folosite ), si la asta am in pdf pentru 36Khz si 100mW.Cm^3 cam 0,2T.

Sm asa cum spuneam este sectiunea miezului folosit, in cazul meu este vorba de 100mm^2.

Numarul de spire in primar este asadar:

Stim deci cate spire trebuiesc in primar, acuma stabilim secundarul si eu voi merge pe redresare cu mediana pentru a folosi mai simplu partea de secundar fara a efectua modificari pe placa, deci 2 infasurari simetrice fazate corespunzator, si asa cum am zis doresc la iesire 35V, pe redresare pica automat ceva tensiune, inca n-am decis ce diode voi folosi dar hai sa zicem 1V, deci pe traf sunt necesare impulsuri de 36V, acuma raportul de transformare este 101/36, adica 2,8, deci secundarele trebuiesc sa fie de 64/2,8, adica 2 infasurari de cate 23 de spire. Avand in vedere curentul de interes mic estimez ca voi avea spatiu de bobinare suficient, in cazul in care curentul dorit este mai mare, e posibil sa nu se detina spatiu suficient pentru 2 infasurari simetrice, deci se va apela la una singura si la redresare in punte.

Mai ramane de stabilit diametrul sarmelor de folosit, pentru primar avem asa cum spuneam cca 1A, admitand o densitate de 4A/mm^2, rezulta o sectiune necesara a conductorului din primar de 0,25mm^2. Alegem conductorul tinand cont de efectul pelicular dat fiind faptul ca frecventa este una relativ mare, si la 36Khz adancimea de patrundere este de circa 0,35mm, deci conductorul folosit poate avea un diametru maxim de 0,35*2, adica 0,7mm, sectiunea necesara anterior presupune un diametru de cam 0,6, deci putem folosi exact sarma din asta de 0,6mm, ne inscriem si la densitate si la adancimea de patrundere. Pentru secundar avem 3A, care la densitatea de 4, presupune o sectiune de 0,75mm^2. In cazul de fata putem merge cu 3 sarme de 0,6 sau cu orice alta combinatie ne va da rezultatul dorit.

Traful de putere este gata:

Am bobinat cu sarma de 0,6 jumatate din primar, apoi secundarele si ultima data cealalta jumatate de primar, pe un rand au incaput 31 de spire si nedorind sa stric un rand pentru o spira am ramas la 62 fata de 64 cat trebuiau, 2 spire in minus este irelevant in cazul de fata. La secundare am bobinat 2 infasurari de cate 22 de spire cu sarma de 1mm. Simetria dintre infasurarile secundare este ok in ciuda faptului ca n-au fost bobinate in paralel, iar cuplajul dintre primar si secundare este unul foarte bun, am masurat inductanta de scapari de 9uH fata de 8,6mH cat are primarul, deci ceva mai mult de 0,1% scapari, suficient de bine zic eu.

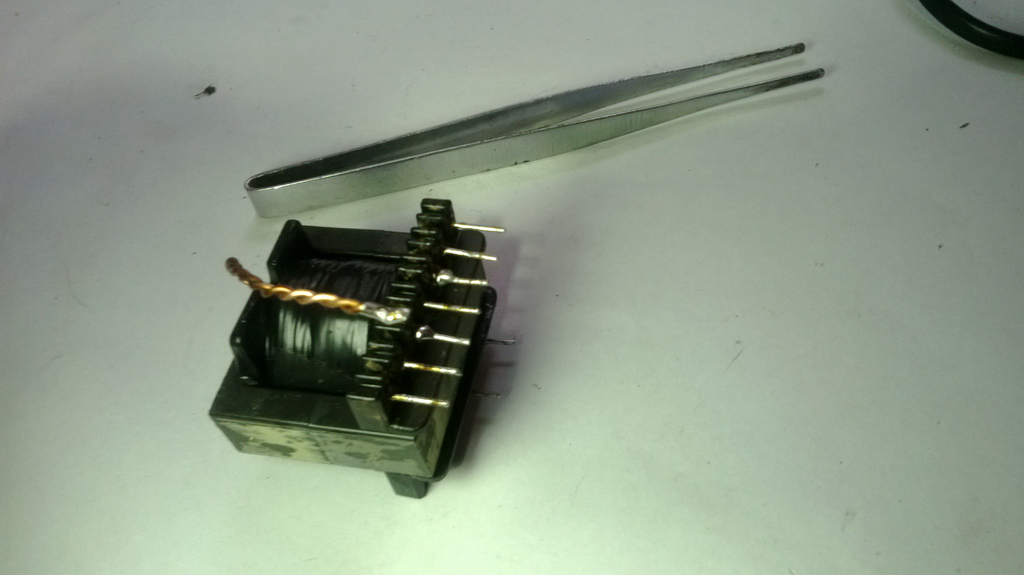

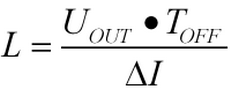

Acum urmeaza calculul inductantei serie necesara stabilizarii, formula este asta:

Unde avem asa:

-Uout este tensiunea stabilizata dorita la iesire;

-Toff este timpul mort din fiecare semialternanta;

-DI ( a se citi Delta-I ) este variatia de curent aleasa pentru inductanta;

Uout asa cum spuneam este tensiunea stabilizata dorita la iesire, aceasta este cea mai curata referinta, aceasta tensiune apare la bornele inductantei la momentul off dintre impulsuri. In cazul meu avem 35V.

Toff este timpul mort din fiecare semialternanta, se exprima in uS pentru a exprima si rezultatul in uH, si pentru a-l determina avem nevoie sa estimam intai o tensiune maxim posibila in primar, tensiune care evident corespunde retelei maxim stiut a fi prezente in cazul fiecaruia si la consumul minim, la mine iau in calcul o retea maxima de 240Vca si ignor pierderile considerand 340Vcc pe electrolitici si jumatate din ei pe primar, adica 170V tensiune maxim estimata in primar.

Acum putem reveni la calculul Toff, si formula este:

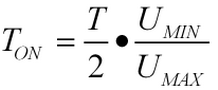

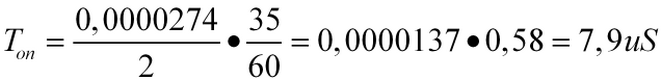

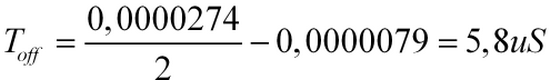

Unde T este perioada corespunzatoare frecventei de lucru, pentru 36,5Khz in cazul de fata T este 27,4uS ( T=1/F ); Ton este cel corespondent tensiunii maxim estimate in primar unde corespunde la randul sau o umplere minima, si este gasit dupa:

La fel ca si mai inainte T este 1/F, Umin este chiar tensiunea dorita la iesire care totodata este si tensiunea minima pe inductanta, iar Umax este tensiunea maxima cu care inductanta este alimentata, aceasta se afla dupa tensiunea maxim estimata in primar si raportul de transformare, la mine am 170V tensiune in primar si 62 spire, fiecare secundar are 22 de spire, deci raportul de transformare este 62/22, adica aproximativ 2,82 care la 170V in primar aduc impulsuri maxime de 60V pe inductanta, si deci rezultatul pentru Ton ar fi:

Acum putem reveni la Toff:

DI asa cum am zis reprezinta variatia de curent aleasa in inductanta, in mod tipic se alege intre 0,15 si 0,3 din Iout ( adica din curentul maxim dorit la iesire ), eu merg pe o medie de 0,2 care din 3A inseamna 0,6A.

Acum avem tot ce ne trebuie pentru calcularea inductantei:

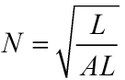

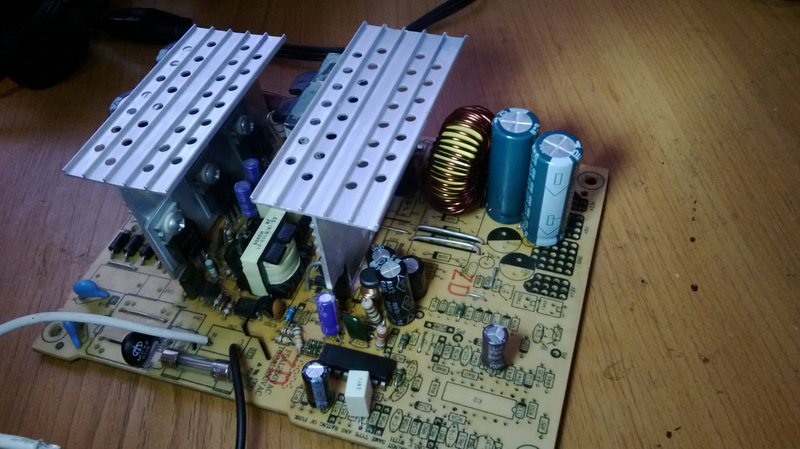

Am realizat inductanta serie, torul este T106-26, unul galben cu alb recuperate din surse ATX, din pdf-ul sau reiese faptul ca inductia la el ( acel AL ) este 93nH/N2, astfel se poate deduce numarul de spire necesar cunoscandu-se faptul ca inductanta creste cu patratul numarului de spire, o formula de calcul poate fi asta:

Unde N este numarul de spire, L este inductanta dorita, care in cazul de fata este 340uH, iar AL este acea inductanta per spira despre care am vorbit mai sus pentru torul asta, in cazul de fata 93nH, si rezultatul ar fi:

Sarma folosita a fost una singura de 1mm ( diametrul ), am bobinat 61 de spire si am obtinut la masuratoare 338uH ( nu am bobinat foarte ingrijit, probabil ca si asta conteaza ) sunt oricum multumit de rezultat. Iata inductanta :

Ar fi de mentionat ca e posibil ca in unele cazuri torurile recuperate sa nu poata fi folosite datorita inductiei in miez care uneori poate ajunge prea sus unde pierderile cresc si permeabilitatea scade riscandu-se saturatia, in cazul meu inductia este undeva pe la 0,28T ( 2800G ), o limita ar trebui sa fie undeva pe la 0,5T ; detalii in acest sens se pot afla din pdf-ul torului folosit, atasez in acest sens link catre o arhiva continand 2 pdf-uri cu date despre torurile cu pulbere de fier:

http://www.mediafire.com/download/rshlu5rdxw5jt0y/Toruri_cu_pulbere_de_fier.rar

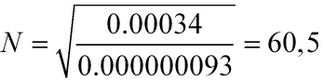

Mai departe trec la partea de control, la TL494 si o schema sumara a acestuia:

Ignor compensarea pentru moment urmand sa revin ulterior detaliat la ea, explicand pentru moment pe scurt schema de mai sus ( pentru cine este interesat ), asadar incepand de la pinul 1, R2 si R3 formeaza divizorul de la intrarea neinversoare cu care se citeste iesirea ; R1 pune inversoarea la referinta ; in cazul asta nu ma voi folosi de al 2-lea AO intern pentru limitare deci il dezactivez punand neinversoarea la masa, si inversoarea la referinta ; C1 si R4 asigura soft-start_ul ; C2 si R5 sunt Ct si respectiv Rt care in cazul de fata asa cum am zis asigura o frecventa pe oscilator de cca 73Khz ; la pinul 12 se face alimentarea pe care o decuplez cu 22u, posibil si 100n, om vedea ; pinul 14 este referinta pe care o decuplez cu un condensator neelectrolitic de 1u ; pinul 13 asigura controlul iesirilor, pentru contratimp este necesar a fi pus la referinta ; iesirile in sine se fac in colectoare, veti observa ca din schema lipsesc rezistentele de sarcina, dar acestea sunt prezente deja pe placa ( in prima schema postata dupa defrisare ); emitoarele evident se pun la masa.

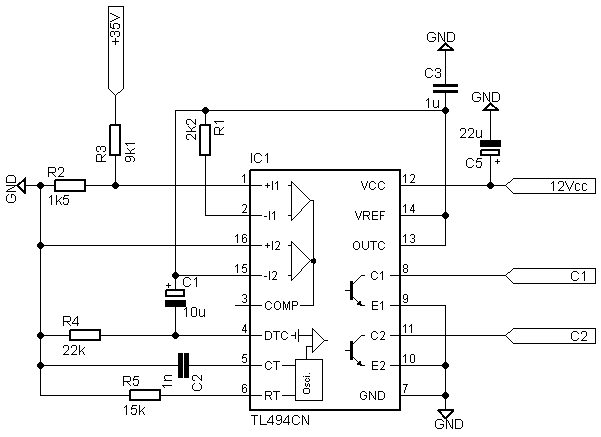

Cam asa arata schema completa a sursei ( asa cum am spus, ignorand auxiliarul ):

Redresarea se face cu F12C20, o dioda dubla la 12A/200V, caderea de tensiune la curentul maxim de sarcina pe ea este undeva putin sub 1V, deci in principiu ok ( evident ca se poate si mai bine dar aici nu randamentul este principalul scop ). Filtrarea se face cu electrolitici Samxon din seria GF, din pdf-ul lor aflu ca cei pe care ii detin eu suporta un riplu de curent maxim de cca 1,7A, riplul de curent in cazul de fata este chiar variatia de curent de pe inductanta, adica 0,6A, adicatelea nu ne intereseaza, suntem oricum departe de limita, tot din pdf-ul lor aflu ca ESR-ul lor este de circa 40m Ohm, la o masuratoare mai mult sau mai putin improvizata rezultatul confirma datele din pdf, asadar folosesc 2 in paralel pentru injumatatirea ESR si am aproximativ 20m Ohm ( un lucru important de stiut in vederea compensarii, se va vedea de ce ). Am pus acum si componentele de la compensare insa nu am trecut si valori, urmeaza sa fie calculate ; deasemeni am inclus si limitarea, una de tip stop cu tiristor simulat insa ramane sa fie calculata ( stabilirea valorilor pentru R19 si R20 ) dupa punerea in functiune a sursei pentru a testa ce tensiune am pe C10 la curentul de 3A la iesire. In caz ca exista dubii, diodele care nu au trecuta valoarea in schema, sunt banalele 4148, motivul pentru care am sters din schema acest lucru este ca ar fi fost prea aglomerata.

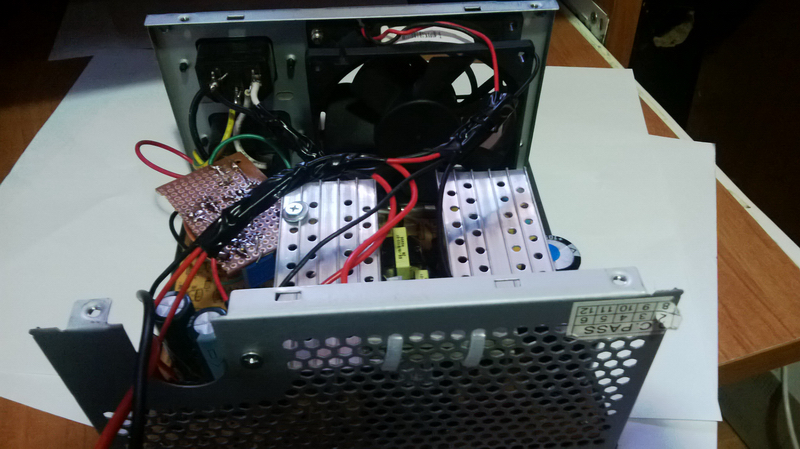

Cam asa arata sursa momentan:

Un subiect tabu pentru multi pare a fi compensarea Amplificatorului de eroare, insasi termenul in sine pare a convinge pe multi sa evite subiectul dar in realitate lucrurile nu-s chiar atat de prohibitive din punct de vedere teoretic, trebuiesc intelese cateva chestii elementare:

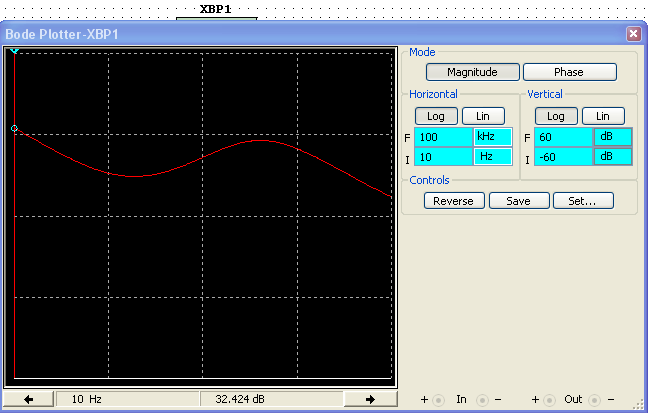

Diagrama Bode este un grafic simplu care reda amplificarea in functie de frecventa si arata in principiu cam asa:

Pe orizontala ( abscisa ) avem frecventa exprimata in Khz pe o scala logaritmica 10hz-100Khz, iar pe verticala ( ordonata ) avem amplificarea in decibeli ( zisa si castig ) pe o scala liniara intre -50 si +90db.

Decada este intervalul dintre o frecventa si alta de 10 ori mai mare, spre exemplu intre 1Khz si 10Khz avem deci o decada, sau intre 10Hz si 100Hz ( 0,1Khz in grafic ) avem o decada… in fine se intelege sper.

Palierul reprezinta o portiune unde amplificarea este liniara sau mai bine zis constanta in gama respectiva de frecvente, este o portiune de caracteristica reprezentata de o linie orizontala dreapta. Palierul arata cam asa :

Polul este o frantura in caracteristica ce creeaza o panta descendenta, adica exact punctul de unde caracteristica incepe sa coboare, panta este de -20 decibeli per decada adica amplificarea scade cu 20 decibeli pe parcursul unei decade. Un grafic simplu ilustrand polul, este punctul de unde palierul ( partea dreapta ) se frange in jos, in cazul de fata pol la 1Khz si o panta de -20db/dec dupa el :

Zeroul este exact invers polului, adica tot o frantura in grafic dar care creeaza o panta ascendenta, adica exact locul de unde linia caracteristicii incepe sa urce, panta creeata de zero este una de +20 decibeli per decada. Ilustrarea grafica, un zero la 1Khz si panta de +20db/dec dupa el :

La caracteristica bode pe langa amplificarea in functie de frecventa, se mai discuta si despre Faza versus frecventa, este defazarea dintre 2 tensiuni, si este reprezentat grafic de o scala logaritmica de frecventa pe abscisa si o scala liniara pe ordonata reprezentand defazarea in grade.

Cunoscand aceste lucruri putem intra direct in subiect. Acuma trebuie stiut ca orice sistem care este bazat pe o anume reactie negativa ( feedback ) trebuie sa indeplineasca anumite Conditii de Stabilitate pentru a functiona corect ( a nu se confunda Stabilitatea cu Stabilizarea, sunt 2 notiuni diferite ). In cazul de fata conditiile sunt: Intersectia caracteristicii Amplificare Vs Frecventa cu linia de 0db trebuie sa se faca pe o panta de -20Db/dec iar faza in acest punct de intersectie sa fie intre +30 si +60 de grade.

Primul lucru pe care trebuie sa-l facem este sa aflam amplificarea initiala de la care se pleaca in trasarea graficului cu caracteristica LC, o formula poate fi aceasta :

-Ai este amplificarea initiala de aflat;

-Up este tensiunea in primar, stim insa de mai inainte ca aceasta poate varia, si ca am ales ca si extreme 101 si respectiv 170V, asadar pentru moment luam in calcul o medie intre cele 2 urmand ca ulterior sa revenim asupra ei pentru a verifica daca extremele pot duce la instabilitate, deci pentru moment Up135V ;

-K este raportul de transformare care se afla impartind numarul spirelor din primar la cel din secundar, eu am 62/22, deci 2,82 ;

-« Alfa » este umplerea maxim estimata, in cazul de fata am spus mai inainte ca este vorba despre 94% ;

-Ua este variatia de tensiune de la iesirea amplificatorului de eroare care aduce o variatie de umplere intre 0 si maxim, in cazul TL494 o variatie de la 0,5 la 3,5V comanda umplere intre 0 si maxim, deci Ua este 3V ;

Rezultatul obtinut este atenuat de divizorul rezistiv de la pinul 1 ( 9k1 si 1k5 ), in cazul de fata atenuarea este de 7, deci amplificarea initiala este de 15/7, adica 2,14, sau 6,6db. In schema avem inductanta serie si electroliticii de filtrare, care impreuna formeaza caracteristica unui filtru trece jos cu frecventa de rezonanta :

Asadar un pol dublu la frecventa de rezonanta a LC de 194Hz, pol care pune dupa el o panta de -40db/dec. In continuare avem ESR-ul condensatorilor de filtrare care asa cum am zis este in principiu o rezistenta inseriata cu condensatorii deci acesta pune un zero la frecventa :

In cazul de fata ESR-ul este 20m Ohm deci zero-ul este pus la cca 4Khz. Acum avem toate cele necesare pentru trasarea graficului continand caracteristica LC :

De aici se poate merge in 2 directii cu corectia necesara ( compensarea propriu zisa ), se poate merge cu intersectia pe panta de -40 dintre Flc si ESR sau se poate merge cu intersectia pe panta de -20db de la ESR, cea de-a 2-a este ceva mai simpla deoarece deja avem panta ceruta de conditiile de stabilitate, corectia trebuie sa contina doar un palier in acea zona de la Flc pana la un pol undeva mai sus, insa nu intotdeauna este indicata aceasta varianta deoarece ESR-ul conzilor poate varia in functie de temperatura destul de mult, mutand astfel zero-ul mai sus sau mai jos de 4Khz, deci se poate ajunge in situatia in care intersectia globalului cu 0db sa nu mai fie pe panta de -20 ceruta ci pe -40, pentru alegerea asta ar trebui sa se cunoasca foarte precis valoarea ESR-ului la temperatura camerei masurandu-se cu un aparat bun si apoi se poate alege o intersectie cat mai conservativa incercandu-se sa se compenseze cat mai bine si variatiile ESR si cele ale tensiunii, pare complicat tare dar nu intotdeauna este asa, uneori intentionat se aleg condensatori cu ESR mai mare care asigura o plaja mult mai buna pentru panta de -20 pusa de acesta, deci micile variatii conteaza mai putin.

Solutia mai sigura este punerea intersectiei pe panta de -40 a LC, dar si aici pot fi probleme in sensul ca daca ESR este prea mare sau Flc este mai mare atunci aceasta panta dintre LC si ESR este destul de mica si face punerea compensarii acolo destul de dificila, o inductanta mai mare la aceeasi capacitate pune polul dublu mai jos in frecventa, apoi un ESR cat mai mic pune zero-ul mai sus, lungind practic aceasta plaja, iar in situatia de fata avem si inductanta relativ mare si ESR ceva mai mic facilitat de punerea a 2 electrolitici in paralel. In cazul de fata avem 1,2 decade intre Lc si ESR, adica suficient zic eu, asadar merg pe panta asta de -40 cu corectia necesara.

Alegem frecventa unde dorim ca globalul sa se intersecteze cu linia de 0db, in cazul de fata merg pe 1Khz fiind aproximativ la jumatatea distantei dintre LC si ESR, mai tarziu verificam daca variatiile alimentarii pot cauza probleme. Trasarea corectiei RC este totusi destul de simpla, stiind ca amplificarile LC cu cele ale corectiei se insumeaza si se obtine globalul, verificam ce amplificare avem pe LC la 1Khz din graficul de mai sus, se poate observa cam -23db, acuma corectia este simplu de aplicat, ea trebuie sa intersecteze frecventa de 1kHz la +23db pentru a aduce globalul la 0 in acel punct, mai stim faptul ca intre frecventa de rezonanta LC si zero-ul pus de catre ESR, corectia trebuie sa puna o panta de +20db/dec pentru ca insumandu-se, sa rezulte un global de -20db/dec, de la Flc in jos corectia trebuie sa puna o panta de -20db pentru ca globalul sa fie tot -20 si aici ( palierul evident ca nu influenteaza panta ), si in fine, de la ESR in sus trebuie un pol pentru o panta de -20 a corectiei care insumata cu cea de -20 a ESR sa creeze o panta de -40db necesara pentru stabilitatea la frecvente mari. Plecam pe grafic de la frecventa de 1Khz si amplificarea de +23db cu o panta de +20db pana la LC, apoi de acolo in jos cu panta de -20 pana la capatul din stanga al graficului, revenim la cei 23db/1kHz si continuam panta de +20db pana la ESR, apoi coboram de acolo cu -20db pana la marginea din dreapta a graficului. Corectia ar arata astfel cam asa ( linia cu verde ) :

Trasarea caracteristicii globale se face plecand de la marginea din stanga tinandu-se cont de faptul ca amplificarile din fiecare punct ( pol sau zero ) se insumeaza si se obtine nivelul la care trebuie sa ajunga caracteristica finala, si deci la inceput avem 6,6db de la linia cu rosu ( caracteristica LC ) plus cam 33db de la corectia RC ( linia cu verde ) deci un total de 39,6db si un punct de la care globalul ( care va fi trasat cu albastru ) pleaca, la frecventa de rezonanta LC de 194Hz avem 6,6db de la LC plus cam 8db de la corectia cu verde, deci un punct la 14,6db, mai departe la ESR ( 4Khz ) avem cam -47 de la rosu si + 36 de la verde, deci un punct la -11db ; globalul trebuie pur si simplu sa uneasca aceste puncte, si de la ultimul se merge cu o panta de -40 pana la marginea din dreapta, ceva de genul asta :

Si practic fara sa ne dam seama, intersectia liniei albastre cu cea de 0db se face chiar la 1Khz, adica exact cum ne-am dorit.

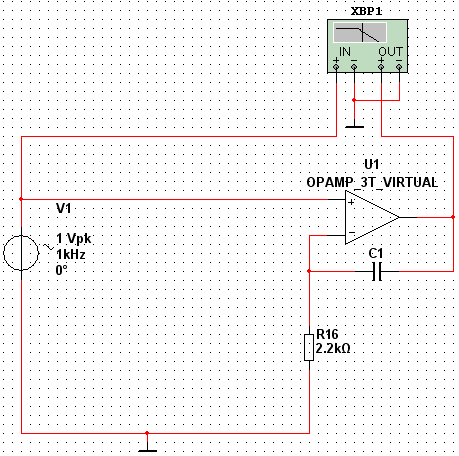

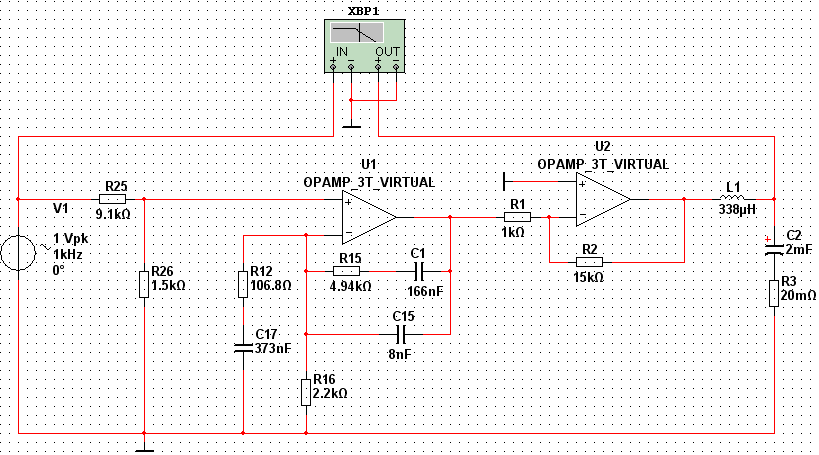

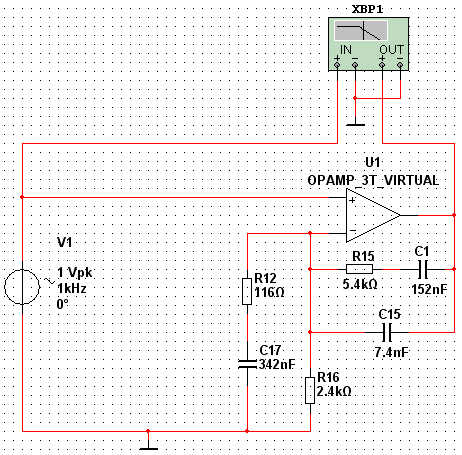

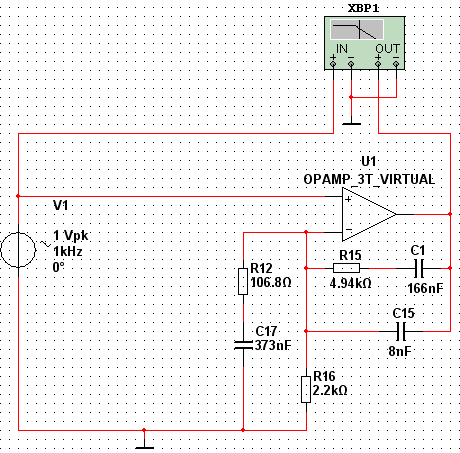

Sa trecem la treaba alegand valorile componentelor din compensare, ma voi folosi de multisim ( V11 ) care este foarte util in asemenea situatii. Trecand peste generalitati in genul mod de functionare AO inversor sau neinversor presupunand ca fac parte din bagajul minim de cunostinte al fiecaruia interesat de domeniul alimentatoare si mergem la interpretarea directa in multisim a sistemului, pentru inceput trebuie reprodusa caracteristica LC trasata in grafice cu rosu. Schema ar fi aceasta:

O sa descriu schema pe scurt, ea are ca referinta masa pentru a fi mai usor de interpretat si reprodus ( in realitate referinta este evident cei 5V de la pinul 14 ), V1 este un generator de semnal sinus care ofera semnalul dorit a fi analizat de Bode Plotter ; voi incerca sa folosesc pe cat se poate notatii ale componentelor identice ca in schema postata anterior pentru a face mai usoara intelegerea lor, asadar R25 si R26 este divizorul identic cu cel din schema; U1 si U2 sunt Amplificatoare Operationale virtuale prezente in multisim la AnalogAnalog_VirtualOpamp_3T_Virtual, sunt operationale virtual ideale si usor de folosit. U1 ilustreaza Amplificatorul de Eroare al TL494 de la pinii 1 si 2, neinversor asa cum este cazul si in schema reala a sursei ; U2 ilustreaza raspunsul sistemului, per ansalmblu sistemul complet este inversor, astfel incat avand AE neinversor, U2 trebuie sa fie Inversor, el ilustreaza amplificarea aceea initiala AI gasita anterior, aici se poate merge in 2 directii, fie se pune o amplificare ca fiind rezultatul AI atenuat de divizor ( situatie in care divizorul nu se mai foloseste inaintea U1 ) fie se merge pe amplificarea gasita initial si se foloseste divizorul, eu merg pe a 2-a varianta, deci amplificare gasita de 15x si divizorul ala inaintea U1 prezent. Restul este simplu, L1 este chiar inductanta din schema la 338uH, C18 este echivalentul celor 2 condensatori de filtrare folositi, ( 1m+1m adica 2m/2000u ), iar R3 ilustreaza ESR-ul condensatorilor pe care l-am evaluat la 20m Ohm, adica 0,02 Ohm.

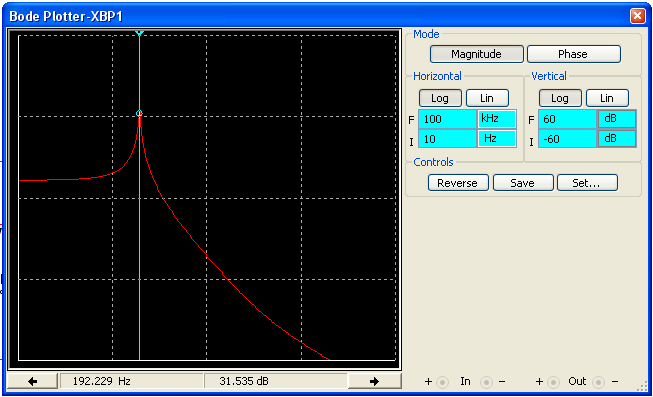

XBP1 este instrumentul cu care monitorizam raspunsul sistemului, cel care ilustreaza in simulator graficele desenate mai sus, are 2 moduri de afisaj, Magnitude care ilustreaza Castigul versus Frecventa, si Phase care ilustreaza Faza versus Frecventa.

Magnitude, la acesta domeniul frecventa de interes se seteaza de la Horizontal unde F este frecventa maxima de interes, in cazul de fata 100Khz, iar I este frecventa minima de interes, punem 10Hz ; gama de interes a Castigului se seteaza de la Vertical, puneti ce valori credeti de cuviinta, in cazul de fata +/-60db mi se pare suficient.

Phase, la Horizontal avem domeniul de frecventa de interes, la fel ca si dincolo trecem 10hz – 100Khz, iar la Vertical domeniul de afisaj al fazei, ne intereseaza un maxim de +/-180gr.

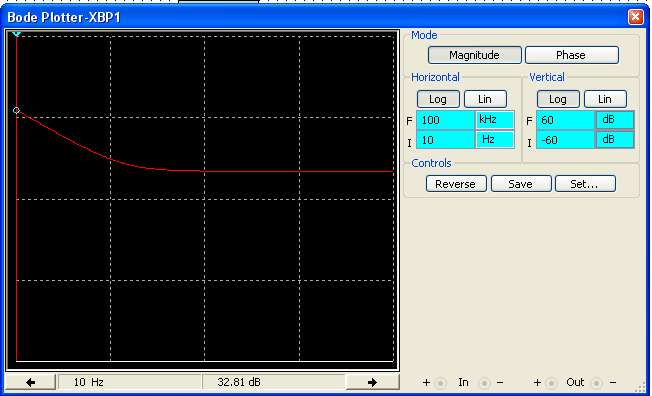

Cam acestea ar fi setarile necesare, acuma se poate rula simularea si analiza raspunsul obtinut care la Magnitude este:

Aceasta trebuie modificata astfel incat sa arate aproximativ cam la fel cu linia cu albastru din graficele de mai sus, si pentru asta trebuie sa lucram la U1 care sa reproduca linia cu verde din acele grafice, asadar pentru moment ne limitam la a monitoriza pe U1 :

Primul pas este punerea pantei de -20 care incepe de la 10Hz pana la rezonanta ( reamintesc ca ma refer aici doar la linia cu verde de pe grafic ), adica punem la 10Hz un pol, si acolo amplificarea vad din grafic a fi cam 33db, deci conform formulei :

Rezulta ca avem o amplificare de 44,6 ori la 10Hz, aceasta scade cu 20db per decada o data cu cresterea frecventei, asa cum am spus mai inainte acesta este comportamentul unui pol, care poate fi reprodus punand un condensator intre iesire si inversoare, si o rezistenta intre inversoare si masa, in cazul de fata R16 din schema ( din care am scos divizorul care pentru moment nu ne intereseaza ):

Reactanta C1 scade o data cu cresterea frecventei deci amplificarea se reduce cu -20db per decada, principiul este asadar asigurat, mai ramane de calculat valoarea sa, asa cum am spus la 10Hz trebuie sa avem o amplificare de 44,6x, reactanta C1 la 10hz necesara este: ![]() , adica:

, adica: ![]() . Din asta putem afla valoarea necesara a C1 pentru aceasta frecventa si reactanta stiind ca

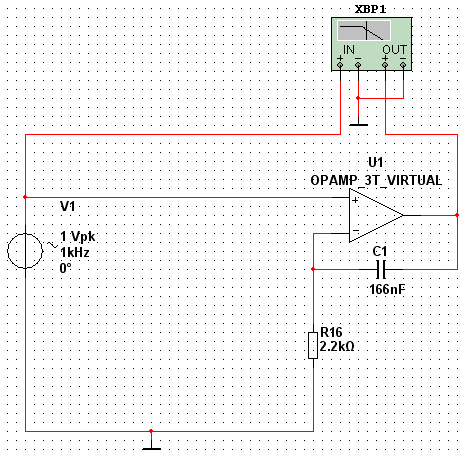

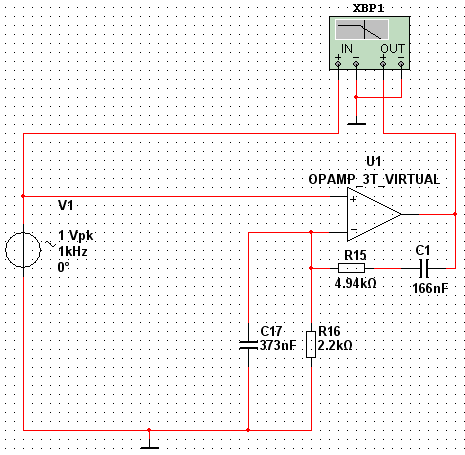

. Din asta putem afla valoarea necesara a C1 pentru aceasta frecventa si reactanta stiind ca ![]() , deci avem pentru C1 166n care nu este tocmai o valoare standardizata, dar pentru moment ramane la aceasta valoare in multisim urmand ca apoi sa alegem si valori mai usor de gasit. Acum schema devine asta in multisim:

, deci avem pentru C1 166n care nu este tocmai o valoare standardizata, dar pentru moment ramane la aceasta valoare in multisim urmand ca apoi sa alegem si valori mai usor de gasit. Acum schema devine asta in multisim:

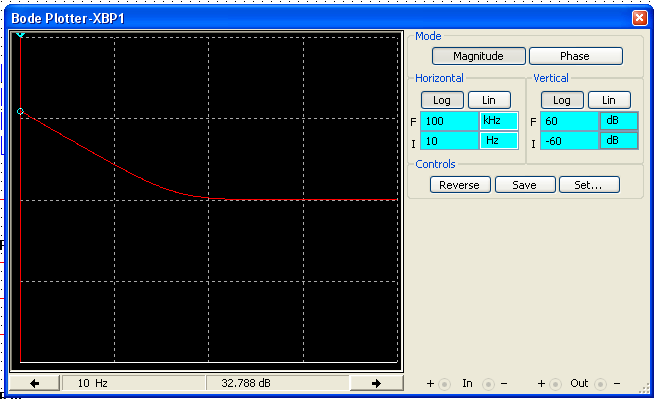

Si raspunsul in bode plotter:

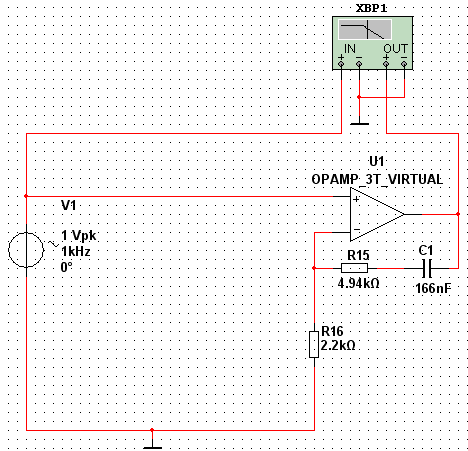

Avem amplificare de cca 33db la 10Hz si panta de -20db/dec dupa, deci este in regula. In graficele anterior postate la corectia cu verde avem in principiu un dublu zero la rezonanta si un dublu pol la ESR, acestea trebuiesc reproduse, incepem evident cu zero-urile, si primul este realizat inseriind o rezistenta ( R15 din schema reala a sursei ) cu C1, care sa puna un palier, de la care se poate pleca cu al 2-lea zero, frecventa de interes este 194Hz, C1 este 166n, deci valoarea rezistentei este ![]()

Schema si raspunsul:

Mai departe urmeaza cel de-al 2-lea zero tot la 194hz, acesta se realizeaza montand un condensator in paralel pe R16 ( C17 din schema sursei ) care condensator datorita scaderii reactantei cu cresterea frecventei, cauzeaza cresterea amplificarii cu panta de +20db/dec, valoarea sa este ![]()

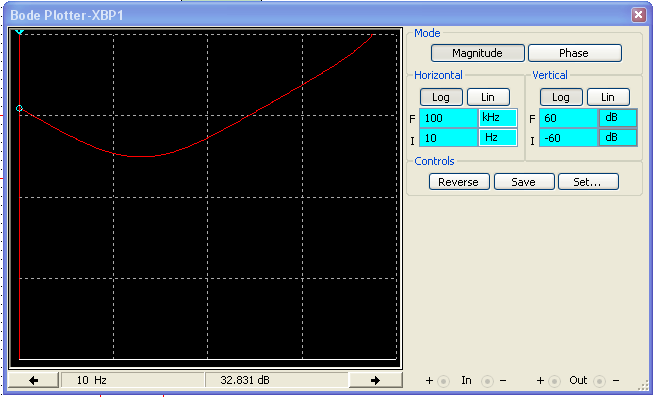

Schema si rezultatul:

In continuare avem polul dublu de la ESR, primul este realizat prin inserierea C17 cu o rezistenta ( R12 in schema sursei ) care sa limiteze scaderea rezistentei dinspre inversoare la masa la un anumit nivel astfel incat limitand si cresterea amplificarii pana la un punct, cu alte cuvinte punandu-se un palier. Valoarea necesara R12 este ![]()

Schema rezultata si raspunsul ar fi:

Ar mai fi de pus ce de-al 2-lea pol, acesta se realizeaza montand un condensator intre iesire si inversoare ( C15 in schema originala ) care practic strapeaza C16 si R15, caracteristica sa de a isi scadea reactanta cu cresterea frecventei limiteaza deci amplificarea la frecvente mari, punand panta aceea de -20db de la final. Valoarea sa este

![]()

Schema si raspunsul:

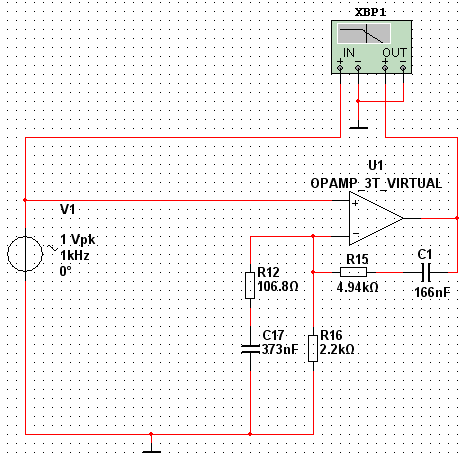

Ne ramane sa completam schema adaugand si U2 si divizorul la loc pentru a observa raspunsul global, intai schema rezultata :

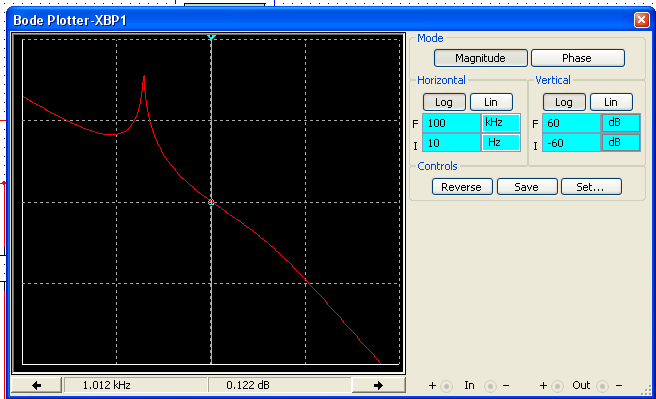

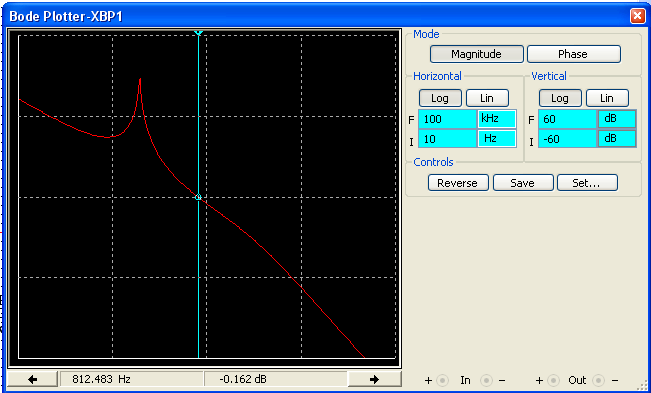

Amplificarea fata de frecventa ce ne intereseaza:

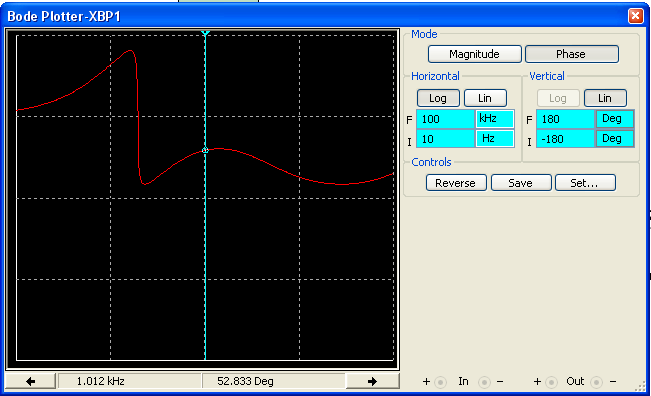

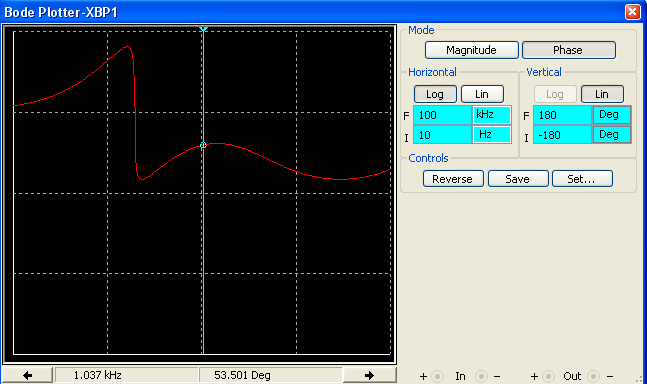

Avem intersectie a globalului cu 0db la 1kHz asa cum ne-am dorit si pe panta de -20db, deci la acest capitol conditiile de stabilitate sunt indeplinite, acum faza in functie de frecventa :

La intersectie ( 1Khz ) avem +52,8gr, sub maximul de 60, deci suntem in limitele ok si aici, cu alte cuvinte compensarea cam asta ar fi la modul ideal. Pare complicat dar va asigur ca nu este asa, in practica este nevoie sa se asimileze anumite chestii de baza care apoi face din asta o rutina si de multe ori graficele nu ne mai trebuiesc, punem direct in multisim caracteristica initiala si de acolo plecam cu ce avem nevoie, sau pentru acuratete se poate pastra metoda desenarii graficelor si dupa aia multisim, e o chestie de preferinta, fiecare cum i se pare mai usor de inteles. Mie unul mi se pare uneori mai dificil de ales valorile standardizate decat calculul compensarii in sine si asta deoarece avem 6 componente toate direct interdependente.

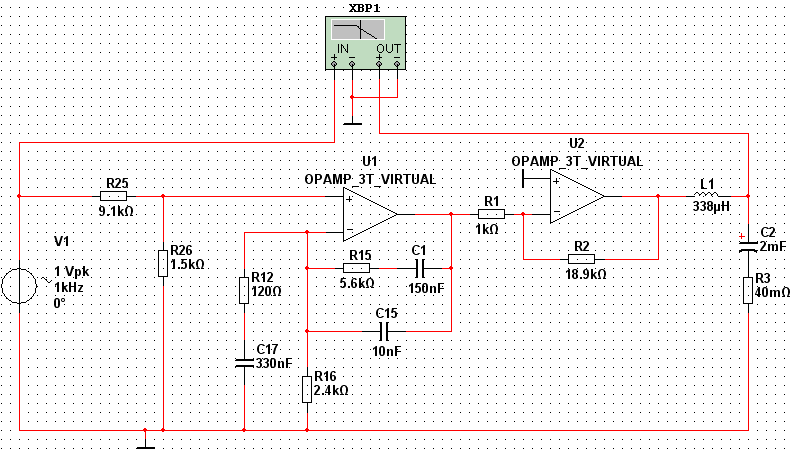

Trecem la ajustarea valorilor componentelor pentru a putea alege unele standard, si evident o luam de la capat cu calculul corectiei numai ca acum stim ce si cum avem de facut deci este mai simplu, nu voi mai repeta formule presupunand ca rolul si formatul lor deja a fost asimilat din postarea anterioara ( daca tot sunt insa nedumeriri legate de unele din ele rog postati si va voi raspunde ), si voi scrie direct rezultatele, deci sa incepem cu polul de la 10hz unde stim ca avem nevoie de o amplificare de 33db, adica circa 44,6x, sa alegem o noua valoare pentru R16 din schemele postate anterior, sa zicem ca am merge pe valoarea standard imediat urmatoare care este 2k4, avem deci cele necesare pentru a calcula reactanta necesara pentru C1, care in cazul de fata este 104,6k, deci C1 rezulta ca tre sa fie 152n, iarasi nu este o valoare standard dar mergem asa si la final stiind valorile tuturor componentelor decidem incotro mergem si comparam rezultatele. Deci R16 2k4 si C1 152n, schema :

Nu mai pun si simularea ca e la fel ca in pagina anterioara, voi atasa doar finalul cu raspunsul global. Acum urmeaza primul zero de la 194 Hz ( rezonanta LC ) care este facut asa cum am scris anterior cu o rezistenta inseriata cu C1, R15 in schemele postate anterior, valoarea sa conform calculelor este 5k4, schema :

In continuare C17 care sa puna impreuna cu R16 al 2-lea zero la 194Hz, valoarea sa ar trebui deci sa fie 342n, schema :

Primul pol de la 4kHz este prin inserierea cu C17 a R12, asadar valoarea sa ar trebui sa fie 116 Ohm, schema :

In sfarsit, C15 care sa puna cu R15 al 2-lea pol la 4kHz, valoarea sa este 7,4n, schema :

Completam din nou schema si verificam raspunsul global:

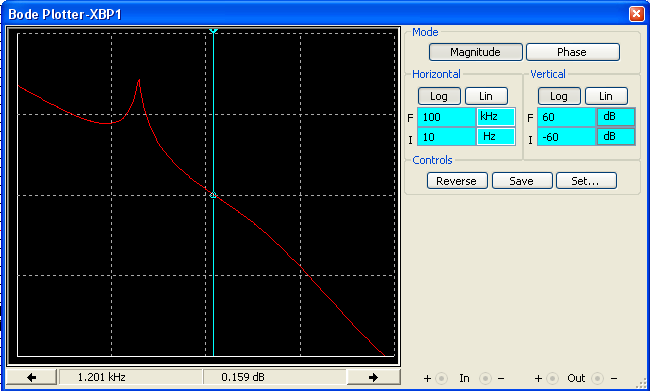

Ambele diagrame arata ok numai ca sunt obtinute din nou cu valori nestandardizate, deci tre sa rezolvam asta, uitandu-ma pe valori as merge pe 150n la C1, 5k6 la R15, 330n la C17, 120 Ohm la R12 si 6,8n la C15, si verificam usor si rapid in multisim daca alegerile sunt sau nu corecte :

Lucrurile ar sta ok, avem intersectie cu 0db pe panta de -20 si la 1kHz, faza ar fi inca sub limita maxima, aici daca se doreste se poate mari C15 la urmatoarea valoare standard pentru a micsora putin faza, la 10n spre exemplu fazarea scade cam pe la +48gr fara a influenta intersectia asa cum este si normal, deci se poate merge asa.

Acuma, spuneam cand ne-am apucat de compensare ca exista anumite variatii care pot influenta rezultatul global, prima ar fi variatia alimentarii care produce la randul sau o variatie a amplificarii initiale acel AI, am ales ca si limite ale tensiunii din primar 101 si respectiv 170V, pentru ele ar corespunde un AI de 11,2 si respectiv 18,9, asta modifica pe verticala pozitia caracteristicii LC trasata cu rosu in grafice, si evident se va modifica si raspunsul global, cum anume putem testa rapid in multisim, intai tensiunea minima in primar 101V corespunzand pentru amplificare 11,2, schema si diagramele bode :

Intersectia s-a mutat la 812hz dar nu-i problema deoarece inca se face tot pe panta de -20, si ar mai fi spatiu sufficient in stanga, deci ok si pentru tensiune si mai mica in primar, fazarea este chiar mai bine acum, +46gr deci in principiu pentru alimentare minima nu estimam nici o problema la compensare.

Sa vedem alimentarea maxima corespunzatoare amplificarii de 18,9, este de la sine inteles sper ca globalul se va muta in directia opusa, schema si diagramele :

Intersectia s-a mutat la 1,2kHz, dar tot pe panta de -20 deci in regula, si aici ar mai fi ceva spatiu pana la panta de -40 care incepe la ESR, ( 4Khz ) deci ar fi in regula. Fazarea la intersectie este pe la 48gr, oricum maximul posibil in configuratia asta tot pe acolo este deci cu alte cuvinte mai sus nu se poate merge adica suntem in regula la ambele limite ale alimentarii.

O alta variatie care poate influenta este cea a ESR care daca se mareste muta zero-ul pus de la 4Khz ceva mai jos, voi estima sa zicem o dublare a valorii sale, adica 40m Ohm si testez asa ca sa vedem ce se intampla :

Intersectia s-a mutat ceva mai sus pe la 1,3Khz insa tot pe panta de -20db numai ca acum rezerva este mult mai mica deoarece zero-ul pus de ESR este acum cam pe la 2kHz insa avand in vedere ca intersectia de acum este la situatia in care alimentarea in primar este cea maxima, nu ne facem griji, stam ok la prima diagrama. Problema apare insa la cea de-a 2-a diagrama unde faza la intersectie este peste limita maxim admisa deci trebuie facut ceva, asta se poate rezolva mergand pe o valoare mai mare la C15, spre exemplu 15n :

Acum lucrurile stau ok, faza este in regula, intersectia la fel, dar asta este cazul alimentarii maxime, sa verificam si alimentarea minima scazand amplificarea la U2 de la 18,9 la 11,2, sa vedem daca aici lucrurile sut inca ok:

Intersectia este inca in regula, si la fel si faza deci teoretic cam asta ar fi, numai ca nu este tocmai asa, datorita variatiei ESR a trebuit sa marim C15, ca sa fim siguri ca inca suntem ok, trebuie sa revenim la valoarea initiala a ESR de 20m Ohm si sa testam din nou limitele de tensiune in primar, respectiv amplificare initiala de 11,2 si apoi de 18,9. Nu mai postez imagini in speranta ca simularea a devenit deja o rutina si a fost inteleasa ci voi posta direct rezultatele, pentru alimentare minima cu c15 la 15n si ESR de 20m Ohm, intersectia s-a mutat la cca 773Hz, ar fi tot ok, faza a scazut la aproximativ 39gr, aici e bine, acum alimentarea maxima releva o intersectie pe la 1,1Khz si o faza de +40gr, iarasi ok asadar.

Am testat si micsorarea valorii ESR la jumatate ( deci 10m Ohm ) comparand cu ambele limite si am gasit ca ar fi ok si aici, pentru alimentare minima intersectia este pe la 773Hz si faza cam 34gr, apoi la alimentare maxima intersectia urca la 1,1kHz si faza acolo este cam 33gr, deci inca in regula.

Asadar se poate observa sper cat de important este acest parametru ESR si cat de mult poate influenta stabilitatea unei surse, nu degeaba spuneam intr-o postare anterioara ca mai dificila mi se pare alegerea de valori standardizate decat calculul in sine, trebuie tinut cont de unele variatii care pot influenta stabilitatea sursei si sa se asigure faptul ca valorile alese compenseaza corect acele variatii.

Schema sursei in sine devine acum cam aceasta :

Inainte sa trec la faza testelor tre sa mentionez ceva, asa cum ati observat valorile condensatorilor de filtrare sunt foarte importante pentru calculul compensarii, uneori sursa modificata va alimenta un montaj care la randul sau va detine poate alt/alti condensatori de filtrare cu propria capacitate si ESR, asta evident ca va influenta comportamentul corectiei, o solutie pentru a izola sursa din acest punct de vedere de consumator este inserierea unei inductante dupa condensatorii de filtrare inclusi in corectie, in general cateva zeci de uH ar trebui sa fie suficient, multe surse din astea de PC au deja pe placa spatiu rezervat unor asemenea inductante micute intre electroliticii de filtrare, este bine sa fie folosite pentru a ne asigura ca nu vom avea probleme, la mine inductanta cu pricina inca nu apare in schema deoarece pe placa nu este prevazuta dar o voi inseria direct pe iesire.

Sa revenim, asadar am revizuit schema sursei si am facut 2 mici ajustari, modificand condensatorul de filtrare de la referinta de la 1u la 47u, motivul este ca valoarea mica a sa ar fi putut influenta corectia unde avem inseriat cu acest condensator pe cel de 330n si rezistenta de 120, cum anume ar fi influentat mai precis nu pot sa ma pronunt cu certitudine dar avand in vedere valorile relativ apropiate am mers pe unul mult mai mare pentru a fi sigur ca nu am probleme. Totodata am adaugat si o rezistenta de sarcina minima pe iesire R27 din schema, una de 470 Ohm/5W, schema deci pentru sursa devenind :

Prima alimentare este bine sa se faca inseriind un bec de 100W cu alimentarea de la retea in cazul in care unele surprize neplacute apar acesta limitand avariile din partea de forta, la mine sursa a functionat perfect din prima dar este bine sa fiti prevazatori. Tensiunea pe iesire este 34,5V ( toleranta rezistoarelor folosite la divizor ), ar putea fi dusa la 35V fix cu un semireglabil dar prefer sa raman asa, mi se pare mai sigur si totodata suficient. Tensiunea la iesire este perfect stabila de la curentul minim pana la cel maxim, iata 2 imagini ilustrand asta :

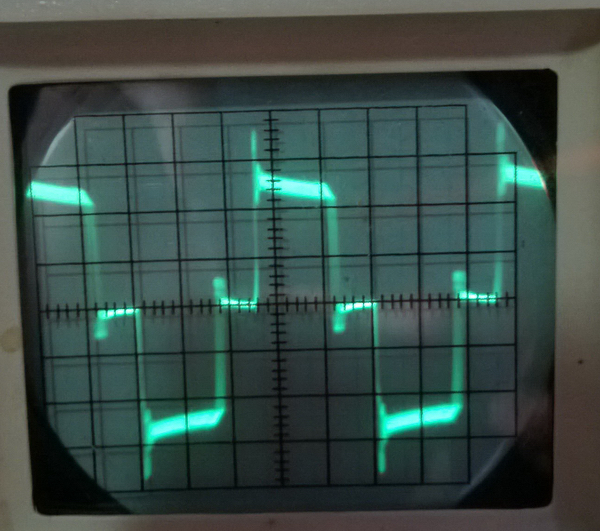

In stanga Voltmetrul iar in dreapta Ampermetrul, la prima acesta indica 0.00A deoarece el este inseriat cu o rezistenta de putere reglabila ceva mai mare pe care o folosesc pe post de sarcina, curentul minim este dictat de rezistenta de 470 de pe placa, la a 2-a imagine am reglat rezistenta pentru cei 3,7A ( o cifra relativ arbitrara ) si tensiunea asa cum se observa a ramas tot 34,5V, deci partea de control isi face treaba ok, iata si cum arata unul din secundare pe osciloscop la acest curent :

Aici ar mai putea fi lucrate snubberele pentru reducerea acelui varf dar avand in vedere dioda de 200V folosita nu-mi fac griji, uneori joaca asta la snubbere poate fi oarecum invaziva pentru placa, sa tot lipesti si sa dezlipesti componente se poate exfolia, eu voi lasa lucrurile asa cum sunt, dar evident daca se doreste se poate ajusta mai ales daca se vor folosi diode de tensiuni mai mici, se ajusteaza valorile in snubbere pana se obtine o amortizare cat mai eficienta a acelor varfuri, se mai pot folosi si transiluri alese pentru o tensiune undeva sub maximul admis de semiconductori si ele vor taia pur si simplu varfurile la nivelul lor… in fine multe se pot face aici, fiecare merge in ce directe prefera. Sursa momentan arata cam asa :

In continuare mai ramane de implementat limitarea, am scos din schema sursei circuitul care se va ocupa cu asta, este vorba despre un tiristor simulat care va fi realizat pe o placuta separata si conectat la placa principala cu ceva fire, iata schema sa unde am pastrat notatiile de la cea completa pentru a se intelege mai usor la ce ma refer :

Schema in sine este destul de simpla dar o voi explica putin, R19 si R20 reprezinta divizorul care preia tensiunea de la mediana trafo driver si comanda partea de limitare, in cazul meu am ales ca punctul in care sursa pune stop sa fie acei 3,7A pentru care pe C10 din schema sursei corespunde o tensiune de 22,5V, aceasta evident va fi si tensiunea pe divizorul R19/R20, am ales deja R20 ca fiind 4k7 si astfel stim si curentul prin divizor avand in vedere faptul ca tranzistorul bipolar se deschide la aproximativ 0,65V intre baza si emitor, deci 0,65/4700=138,3uA, sau 0,0001383A, asadar pe R19 ar fi tensiunea de la c10 minus cei 0,65, adica 21,85V si deci o rezistenta de 21,85/0,0001383=158k, care nu este tocmai o valoare standard, se poate merge pe modificarea R20 pana se obtine o valoare mai aproape de standard la R19 sau se poate pastra R20 la 4k7 si la R19 sa se foloseasca o rezistenta de 150k plus un semireglabil serie de 10k, eu merg pe semireglabil, deci 150k+10k.

Tiristorul in sine este compus din Q6 si Q7, si amorsarea sa o realizeaza Q5 care atunci cand se atinge pragul prestabilit se deschide si pune R23 la masa, asta aduce un anumit curent prin divizorul pe care R23 il alcatuieste cu R24 si deschide Q7, acesta alimenteaza prin intermediul R22, baza Q6 care se deschide si pune la randul sau R23 la masa, din acest moment tiristorul este amorsat si starea Q5 nu mai conteaza, cei 2 tranzistori se automentin deschisi, prin D14 si D15 se aduce o tensiune la pinul 4 ( ceva mai mult de 3V ) care forteaza blocarea trenului de impulsuri de pe iesiri si deci sursa este blocata, reluarea functionarii putandu-se face dupa resetarea limitarii prin oprirea alimentarii sursei de la retea si se asteapta ceva timp pana la descarcarea condensatorilor, in general cateva secunde. Acum schema completa a sursei devine aceasta :

Sursa este stabila, tensiunea se mentine ok pe intreaga gama de curent necesara, temperatura radiatoarelor este ok ( destul de mica ), mai ramane sa pun limitarea pe o placuta si sa o montez.

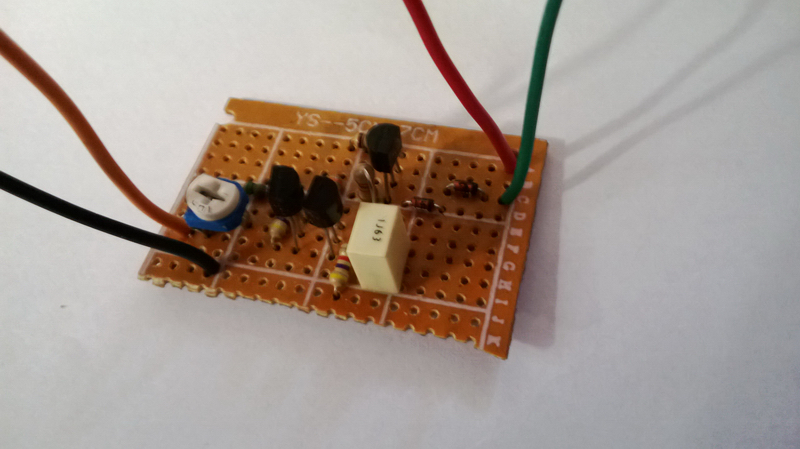

Am pus la punct si placuta de limitare, aceasta ar fi:

Am reglat-o si apoi am testat, protectia isi face treaba perfect, la scurt pe iesire sursa se blocheaza de fiecare data, am fixat-o apoi pe unul din radiatoare si am purces la completarea sursei, cateva poze :

Ca fapt divers la cca 3,8A curent de sarcina (fata de 3A la cat ar trebui sa lucreze in mod normal) am masurat un randament de aproximativ 90% ceea ce mi se pare chiar ok. Asa cum am zis si anterior, tensiunea este perfect stabila pe intreaga gama de curent de interes ( adica nu se modifica catusi de putin ), ar mai fi resurse pentru curent chiar mai mare, as estima un posibil 5A fara prea mari dificultati, sursa este stabila deci bucla de reactie dimpreuna cu compensarea isi fac treaba perfect, asadar munca minutioasa la calcule da rezultate.

Cam acesta ar fi finalul modificarilor si al proiectului in sine, cu speranta ca articolul a ajutat, ma retrag aici si va doresc multe realizari.

Numai bine.

Marian Berbece.

Comentarii

Trimiteți un comentariu